# ELECTRONICS JR STRONIC

OW TO HARNESS FRAM SYSTEM DESIGN

VOLUME 114, ISSUE 1865

MAY 2008 £4.60 www.electronicsworld.co.uk

70959

D THE FPGA DESIGN FLOW ti N D HRST

> VIRTUES AND BENEERTS OF **OPEN-SOURCE-SOFTWARE**

# At the heart of modern mications

TECHNOLOGY NEWS FROM THE MWC IN BARCELONA

MODEL-BASED DESIGN FOR MECHATRONIC

SOFTWARE SYSTEMS

LETTERS CFLS VERSUS ORDINARY BULBS -THE BATTLE HAS BEGUN

ALSO IN THIS ISSUE: THE TROUBLE WITH RF: SEEING THROUGH WIRELESS TRENDS

Peak Electronic Design Limited West Road House, West Road, Buxton, Derbyshire, SK17 6HF

tel. 01298 70012 fax. 01298 70046 www.peakelec.co.uk sales@peakelec.co.uk

## Handheld Test Gear - Cool, Smart.

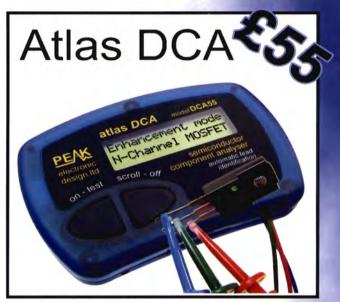

Atlas DCA - Model DCA55 Semiconductor Analyser Identifies type and pinout! Connect any way round.

Measures gain, junction characteristics and more.

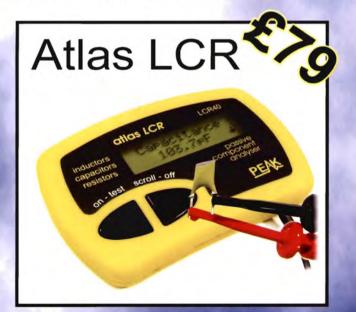

Atlas LCR - Model LCR40 Inductor, Capacitor, Resistor Analyser Automatic part identification, automatic frequency selection and auto ranging!

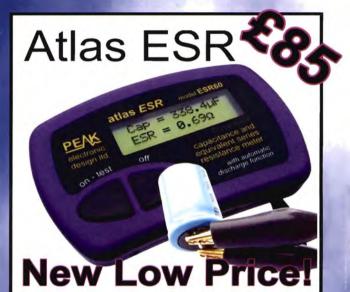

Atlas ESR - Model ESR60 ESR and Capacitance Meter

Measures capacitance, ESR (in-circuit too!). Automatic controlled capacitor discharge feature!

Atlas SCR - Model SCR100 Triac and Thyristor Analyser Connect any way round, auto lead identification. Auto gate test current from 100uA to 100mA.

UK: Please add £1.00 p&p to your order. Prices include UK VAT. Please see website for overseas pricing.

### Electronics World CONTENTS

### 05 EDITOR'S COMMENT

WHAT'S WRONG WITH THIS PICTURE?

### 06 TECHNOLOGY

### 10 TOP TEN TIPS

### 12 COMPANY PROFILE

AT THE HEART OF MODERN COMMUNICATIONS by Juan Pablo Conti

### 16 **ROHS**

Gary Nevison answers readers' questions relating to the RoHS, WEEE and EuP directives, and REACH

### **17 THE TROUBLE WITH RF...**

SEEING THROUGH THE WIRELESS TRENDS by Myk Dormer

### 19 INSIGHT

2008 - THE YEAR OF POLYMER ELECTRONICS? by Dr Alec Reader

### REGULARS

### **39 LETTERS**

**40 CIRCUIT IDEAS**

### 44 UKDL

IS 3-D FINALLY ON ITS WAY TO A SHOP NEAR YOU? DO YOU WANT IT IF IT IS? by Chris Williams

### 47 TIPS 'N' TRICKS

### 51 BOOK REVIEW

### 52 PRODUCTS

### FEATURES

- 20 DESIGNING MISSION-CRITICAL SYSTEMS USING OMG SYSML Matthew Hause shows how OMG SysML artifacts can be used on mission-critical applications

- 23 MODEL-BASED DESIGN FOR MECHATRONIC SYSTEMS Tony Lennon explains the benefits and why model-based design is the tool of choice for system-level design of mechatronic systems

- 27 UN-DOCUMENTED CODE AND THE ELECTRONICS INDUSTRY Mark Tolliver discusses the virtues of open-source software but also the pitfalls for modern firms trying to comply

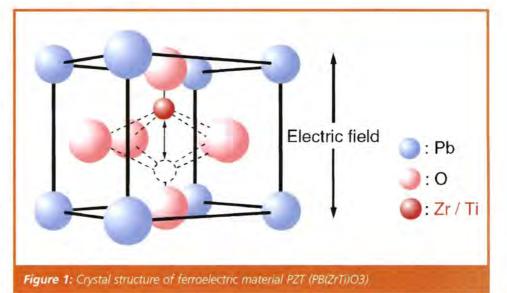

- **29** OPENING UP OPPORTUNITIES IN SYSTEM DESIGNS Wolf Fronauer looks at why ferroelectric random access memory (FRAM) is becoming increasingly popular with system designers

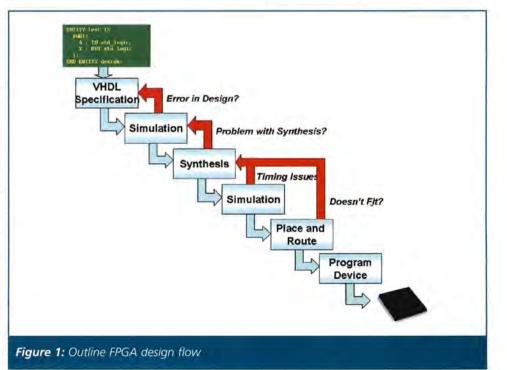

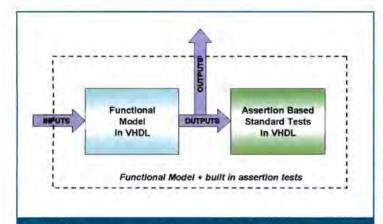

- **32** UNDERSTANDING THE FPGA **DESIGN FLOW** Dr Peter R. Wilson goes into detail of the practical aspects of successfully completing an FPGA design using VHDL and a successful simulation

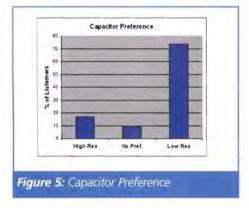

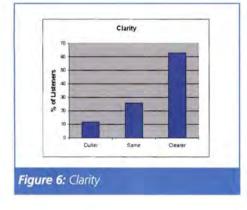

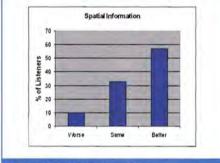

- **36 THE EFFECTS OF AUDIO CAPACITORS ON** SOUND QUALITY

Paul Dodds goes over the findings of a recent research that established the effect of the capacitor's properties on the quality of sound

Quasar Electronics Limited PO Box 6935, Bishops Stortford CM23 4WP, United Kingdom Tel: 0870 246 1826 Fax: 0870 460 1045 E-mail: sales@quasarelectronics.com Web: www.QuasarElectronics.com

Postage & Packing Options (Up to 0.5Kg gross weight): UK Standard 3-7 Day Delivery - £3.95; UK Mainland Next Day Delivery - £8.95; Europe (EU) - £6.95; Rest of World - £9.95 (up to 0.5Kg) Order online for reduced price UK Postage! We accept all major credit/debit cards. Make cheques/PO's payable to Quasar Electronics. Prices include 17.5% VAT. Call now for our FREE CATALOGUE with details of over 300 kits, projects, modules and publications. Discounts for bulk quantities

**Motor Drivers/Controllers**

Here are just a few of our controller and driver modules for AC, DC, Unipolar/Bipolar stepper motors and servo motors. See website for full details.

#### PC / Standalone Unipolar

Stepper Motor Driver Drives any 5, 6 or 8-lead unipolar stepper motor rated up to 6 Amps max. Provides speed and direc-

tion control. Operates in stand-alone or PCcontrolled mode. Up to six 3179 driver boards can be connected to a single parallel port. Supply: 9Vdc. PCB: 80x50mm. Kit Order Code: 3179KT - £12.95 Assembled Order Code: AS3179 - £19.95

#### **Bi-Polar Stepper Motor Driver**

Drive any bi-polar stepper motor using externally supplied 5V levels for stepping and direction control. These usually come from software running on a computer.

Supply: 8-30Vdc. PCB: 75x85mm. Kit Order Code: 3158KT - £17.95 Assembled Order Code: AS3158 - £27.95

#### **Bi-Directional DC Motor Controller (v2)**

Controls the speed of most common DC motors (rated up to 32Vdc, 10A) in both the forward and reverse direction. The

range of control is from fully OFF to fully ON in both directions. The direction and speed are controlled using a single potentiometer. Screw terminal block for connections Kit Order Code: 3166v2KT - £17.95 Assembled Order Code: AS3166v2 - £27.95

#### DC Motor Speed Controller (100V/7.5A)

Control the speed of almost any common DC motor rated up to 100V/7.5A. Pulse width modulation output for maximum motor torque at all speeds. Supply: 5-15Vdc. Box supplied.

Dimensions (mm): 60Wx100Lx60H. Kit Order Code: 3067KT - £13.95 Assembled Order Code: AS3067 - £21.95

Most items are available in kit form (KT suffix) or assembled and ready for use (AS prefix).

### **Controllers & Loggers**

Here are just a few of the controller and data acquisition and control units we have. See website for full details. Suitable PSU for all units: Order Code PSU445 £8.95

#### 8-Ch Serial Isolated I/O Relay Module

Computer controlled 8channel relay board. 5A mains rated relay outputs. 4 isolated digital inputs. Useful in a variety of control and sens-

**Credit Card**

Sales

ing applications. Controlled via serial port for programming (using our new Windows interface, terminal emulator or batch files). Includes plastic case 130x100x30mm. Power Supply: 12Vdc/500mA

Kit Order Code: 3108KT - £54.95 Assembled Order Code: AS3108 - £64.95

#### Computer Temperature Data Logger

4-channel temperature logger for serial port. °C or °F Continuously logs up to 4 separate sensors located 200m+ from board. Wide

range of tree software applications for storing/using data. PCB just 45x45mm. Powered by PC. Includes one DS1820 sensor. Kit Order Code: 3145KT - £17.95 Assembled Order Code: AS3145 - £24.95 Additional DS1820 Sensors - £3.95 each

#### **Rolling Code 4-Channel UHF Remote**

4 channels. Momentary or latching relay output. Range up to 40m. Up to 15 Tx's can be learnt by one Rx (kit in-

cludes one Tx but more available separately). 4 indicator LED 's. Rx: PCB 77x85mm, 12Vdc/6mA (standby). Two and Ten channel versions also available. Kit Order Code: 3180KT - £44.95 Assembled Order Code: AS3180 - £54.95

Call your phone number using a DTMF phone from anywhere in the world and remotely turn on/off any of the 4 relays as de-

sired. User settable Security Password, Anti-Tamper, Rings to Answer, Auto Hang-up and Lockout. Includes plastic case. Not BT approved 130x110x30mm Power 12Vdc. Kit Order Code: 3140KT - £54.95 Assembled Order Code: AS3140 - £69.95

Infrared RC Relay Board

range. 112x122mm. Supply: 12Vdc/0.5A Kit Order Code: 3142KT - £47.95 Assembled Order Code: AS3142 - £59.95

### **PIC & ATMEL Programmers**

We have a wide range of low cost PIC and ATMEL Programmers Complete range and documentation available from our web site.

Programmer Accessories:

40-pin Wide ZIF socket (ZIF40W) £14.95 18Vdc Power supply (PSU010) £18.95 Leads: Parallel (LDC136) £395 / Serial (LDC441) £3.95 / USB (LDC644) £2.95

#### NEW! USB & Serial Port PIC Programmer

USB/Serial connection. Header cable for ICSP. Free Windows XP software. Wide range of supported PICs - see website for

complete listing. ZIF Socket/USB lead not included. Supply: 16-18Vdc. Kit Order Code: 3149EKT - £39.95 Assembled Order Code: AS3149E - £49.95

#### NEW! USB 'All-Flash' PIC Programmer

USB PIC programmer for all 'Flash' devices. No external power supply making it truly portable. Supplied with box and Windows Software ZIF Socket and USB lead not included

Assembled Order Code: AS3128 - £44.95

#### "PICALL" PIC Programmer

'PICALL" will program virtually all 8 to 40 pin serialmode AND parallel-mode (PIC16C5x family) programmed PIC micro control-

lers. Free fully functional software. Blank chip auto detect for super fast bulk programming. Parallel port connection. Supply: 16-18Vdc. Assembled Order Code: AS3117 - £24.95

#### ATMEL 89xxxx Programmer

Uses serial port and any standard terminal comms program. Program/ Read/ Verify Code Data, Write Fuse/Lock Bits, Erase and

Blank Check. 4 LED's display the status. ZIF sockets not included. Supply: 16-18Vdc. Kit Order Code: 3123KT - £24.95 Assembled Order Code: AS3123 - £34.95

www.QuasarElectronics.com Secure Online Ordering Facilities • Full Product Listing, Descriptions & Photos • Kit Documentation & Software Downloads

### COMMENT

#### EDITOR:

Svetlana Josifovska Email: svetlana.jasifovska@stjohnpatrick.com

PRODUCTION EDITOR/DESIGNER: Tim Wesson

DISPLAY SALES EXECUTIVE: Matthew Dawe TEL: +44 (0) 20 7933 8999 Email: matthew.dawe@stjohnpatrick.com

EDITORIAL DIRECTOR: Melony Rocque

SALES DIRECTOR: Chris Cooke

#### PUBLISHER: John Owen

### SUBSCRIPTIONS:

Dovetail Services 800 Guillat Avenue, Kent Science Park, Sittingbourna, Kent, ME9 8GU TEL: +44 (0) 844 844 0230 Email: saintjohnpatrick@servicehelpline.co.uk

#### SUBSCRIPTION RATES:

1 year: £46 (UK); €120 (Europe); \$145 (US & worldwide)

#### NEWSTRADE:

Distributed by Seymour Distribution Ltd, 2 East Poultry Avenue, London, EC1A 9PT +44 (0) 20 7429 4000

PRINTER: William Gibbons Ud

### WHAT'S WRONG WITH THIS PICTURE?

ate last year the UK's industry regulator Ofcom initiated a consultation on its proposals for upgrading Freeview (a free digital service) for High Definition Television (HDTV). Digital TV Group, or DTG, is an industry association for digital TV in the UK, and it is just one of the organisations to comment on that consultation.

While it seems to welcome Ofcom's recognition that HDTV public service broadcasts should be provided for on the digital terrestrial platform (DTT), it also expressed concerns that the regulator's proposals could seriously compromise DTT's long term viability and the platform most adopted by UK viewers and consumers that is Freeview. In turn, DTG is calling for a comprehensive national strategy for HDTV, encompassing all television platforms.

Ofcom proposes that the HDTV service on DTT will be restricted to only between three and four channels. But, this will inevitably threaten the picture quality of HDTV programming, as well as the reach of the existing standard definition channel line-up. If HDTV is broadcast on less number of channels this will save on spectrum (which I assume will then be sold on for a hefty profit to others), but this defies the object of the whole exercise of having HDTV in the first place, which by default should be a lot higher in guality than anything seen to date.

DTT is still the UK's most popular digital television platform with over 14 million units sold and many are led to believe that HDTV will offer unmissable viewing experience. If that experience is no longer to be, then why are millions of viewers shelling out thousands of pounds on 'HD-ready' plasma and LCD screens?

So far there has been heavy promotion of all services digital (radio, TV etc) but why is Ofcom making a Uturn when it comes to the quality of such services. And why is the industry (chip makers, set-top box manufacturers, television set suppliers etc) not kicking up some fuss over this?

Some years ago, the UK (and in particular the BBC), was at the forefront of adopting, testing and promoting new broadcast technologies, but a little under ten years and we are seeing a completely different and, excuse the pun, very fuzzy picture emerging.

It will be disheartening to see the UK which once stood at the helm of new broadcast technologies end up with second class HDTV services.

### Svetlana Josifovska Editor

Check out Electronics World's new website by clicking on www.electronicsworld.co.uk

Electronics World is published monthly by Saint John Patrick Publishers Ltd, 6 Laurence Pountney Hill, London, EC4R 0BL.

Disclaimer: We work hard to ensure that the information presented in Electronics World is accurate. However, the publisher will not take responsibility for any injury or loss of earnings that may result from applying information presented in the magazine. It is your responsibility to familiarise yourself with the laws relating to dealing with your customers and suppliers, and with safety practices relating to working with electrical/electronic circuitry – particularly as regards electric shock, fire hazards and explosions.

### TECHNOLOGY News

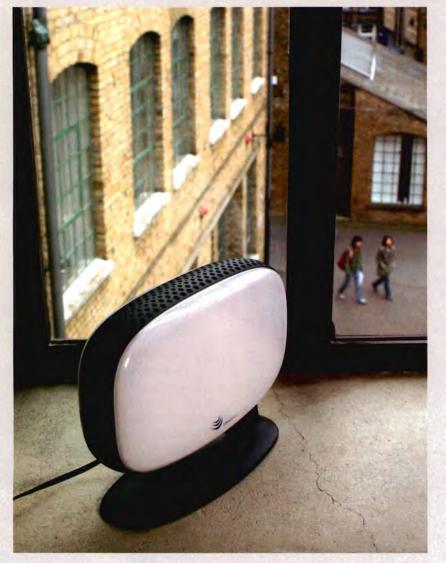

### Femtocells create buzz but leave questions unanswered

The biggest challenge in femtocell use is who is going to meet the cost of the subscriber box

Mobile operator O2 is starting trials of femtocell technology in the UK with plans for a commercial launch next year. This announcement at the Mobile World Congress in Barcelona created a buzz around the show as exhibitors jostled to display their femtocell offerings.

In a way, this is strange given that the introduction of femtocells is almost an admission of failure by the mobile operators, which for a long time have boasted about how widespread their coverage is.

Users though have known for a long time that, while city centre coverage is normally fine, residential coverage is patchy to say the least. The idea behind femtocells is that each home can buy a box that will boost mobile phone coverage in their own home.

But there are problems. First, and the big headache at the moment, is

who will pay? Consumers are not going to be over happy about splashing out between \$100 and \$200 (rough estimates from different firms at the show) for a box to give them the sort of reception they are meant to be getting anyway.

"The biggest challenge is who is going to meet the cost of the subscriber box," said Rakesh Vij, assistant vice president of communications software company Aricent. "Once the volume goes up, the price will drop, but someone still has to pay."

Some believe that the mobile phone operators themselves will subsidise the cost as a way of keeping subscribers on their network. But what about homes in which different people are on different networks? A single box can handle that and boost the coverage for all the networks it can see, however it is felt that a network operator is unlikely to fund a box that will boost the reception for its rivals and will insist that the boxes are locked to its network. Do not be surprised therefore to see "unlock your box" signs springing up next to the "unlock your phone" signs in shops around the country.

Another option will be mobile virtual network operators (MVNOs) that have roaming agreements with the different main operators and will sell multi-operator boxes.

As to the O2 trial, this is being done in partnership with NEC and Ubiquisys, which is making the boxes.

"The technology is ready," said Will Franks, chief technology officer at Ubiquisys. "We have done our own trials. We have made 1000 boxes so far and they are out there being tested."

### News TECHNOLOGY

### Mobile phone jackets for each season

"Tiny, slick and stylish," says Modu about its latest mobile phone

Israeli company Modu believes it has solved the problem of people who like to keep up with the latest mobile phones trends and yet are stuck with upgrading only every 12 to 18 months.

The company was showing at the Mobile World Congress in Barcelona what it claims is the world's smallest and lightest mobile phone (a claim that marketing vice president Tzahi 'Zack' Weisfeld said was verified by the Guinness Book of Records) and that the phone would fit into different jackets to give it different functionalities.

The company was quick to point out that this was not just changing the cover; that is a modular phone that's designed to be slotted into various attachments such as clothing, briefcases or other consumer devices. The device allows message texting, MP3 playback and is Bluetooth enabled among others.

Inserting the phone into a jacket can transform its functionality. City jackets are a good example. If the user is roaming in a city they are not familiar with, they could buy a jacket for that city. The phone would be inserted into it, and then the screen would display maps of the city with information about restaurants and points of interest. Alternatively, the phone could be a business email terminal with qwerty keyboard during the working day. A quick switch of jackets after work and it becomes an MP3 player with high quality speakers.

Each jacket contains an ASIC that controls the interface between the jacket and the phone. For more advanced jackets, such as those with GPS facilities for example, the jacket will contain an extra co-processor to handle that functionality.

"I suspect people will start launching seasonal collections," said Weisfeld. "It takes a lot of time and money to make a phone and certify it. It is a lot less to make a jacket and you don't have to certify it."

The company has already signed deals with some operators and commercial launches are scheduled for October in Brazil, Israel, Italy and Russia, with other countries to follow.

### IN BRIEF

UK consultancy and engineering firms are among the best to work for, according to a recent survey by the Association for **Consultancy and Engineering. These firms** are now close to financial services companies as the most successful sector in the 2008. The Association's chief executive Nelson Ogunshakin said: "UK consultancy and engineering firms are world leaders in design, business practices, professionalism, profitability and staff happiness." "Those of us in the industry understand that an engineering career is unique. It offers the opportunity to contribute to processes that could affect how people live in hundreds, perhaps thousands of years. It is not surprising that the staff at engineering firms feel so fulfilled," he said.

Following the launch of the science and innovation strategy by the UK's government in March, the CBI's Director-General, Richard Lambert said that the government talks the "right kind" of talk but needs to follow it with action.

"It is important we look at our 'innovation ecosystem' as a whole and don't just think of innovation as 'doing science' or 'inventing things'," said Lambert.

He added that the government can play a big role by harnessing some of its massive £150bn annual spend on goods and services and helping to kick-start new markets for innovative ways of doing things and tackling big issues such as climate change and security.

● The worldwide market for semiconductor assembly and test services (SATS) grew for the sixth consecutive year in 2007, according to industry analyst firm Gartner. Worldwide SATS revenue was up 7.4% at \$20.6bn. For the sixth year in succession, the SATS market continued to outpace the overall semiconductor market by more than 50% (overall semiconductor revenue grew 2.9% in 2007).

Packaging, assembly and test services have become important in the total semiconductor industry because a growing percentage of the total industry revenue is now attributed to this segment. The outsourcing portion of this back-end manufacturing process, known as SATS, has grown steadily since the recession of 2001.

### Mobile phone security keeps in tune

A method of verifying that the person talking on a mobile phone is really who they say they are will be music to the ears of banking and other financial institutions.

The clever technology comes from Yves Eonnet, who was once head of innovations at Schlumberger's smartcard division but now runs Tagattitude, a company he set up to offer a service to let mobile phone users sign transactions securely.

Using audio signal processing, the system combines music and passwords to verify a user's identity. With an online transaction, the user enters a log-in and password onto a web site in the normal way. Two seconds later, the mobile phone rings. The user answers it and the web site then plays music that contains an encrypted one-time password that is heard down the phone line.

"This guarantees that your phone is in front of the web page," said Eonnet. The system can also be used to authenticate a user in front of a bank ATM money machine and even to authorise a transaction between two users without them even knowing who each other is. One user can enter the amount to pay on his or her phone and the recipient does the same on their phone and then the two phones play a signal to each other to verify the transaction.

"The phone becomes like a bank card for people," said Eonnet. "This is important for developing countries where most people don't have bank accounts. They can use their phone with a prepaid account."

There are pilot schemes running in three countries in Africa, including the Ivory Coast, done through France Telecom's Orange mobile phone subsidiary. French bank Crédit Agricole is also about to implement the technology for online transactions.

NSDT<sup>TM</sup> Platform architecture

Figure 1: Face2 FaceTM overall architecture

The platform which allows the mobile phone to become a bank card for users

### WORLD'S SMALLEST IS ABOUT TO GET SMALLER

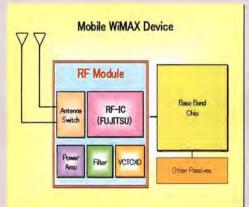

Fujitsu was showing off its mobile WiMax baseband chip at Mobile World Congress in Barcelona but was promising more to come before the year is out.

The WiMax RF module fits into a 15x15mm form-factor and is claimed to be the world's smallest to contain all the RF circuits needed for mobile WiMax, including RF IC antenna switches, power amplifier, filters and oscillator circuits.

But Manfred Mettendorff, senior marketing manager, said

Block diagram of Fujitsu's WiMax IC solution

that by July or August this year the firm would have its second generation chip that would combine all that with power management circuitry and memory in the same formfactor. This will be done using 65nm process technology compared with 90nm for the existing chip.

"The current one is targeting PC applications," he said."The new one will target batterydriven mobile devices because of its lower power consumption.

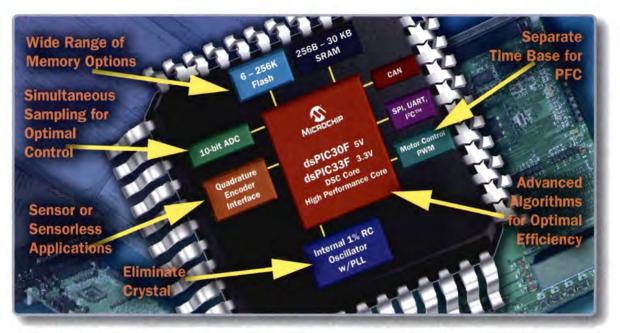

### More Efficient 3-Phase Motor Control

### Explore the new motor control solutions from Microchip

Are you considering moving to brushless motors, eliminating costly sensors or adding PFC? Let Microchip show you how to improve your efficiency, lower noise, reduce your form factor and explore cost reduction options. Visit www.microchip.com/DSCMOTOR and discover Microchip's comprehensive motor control solutions, featuring 16-bit Digital Signal Controllers, free software, technical training, development tool discounts and more!

|                       | Motor Control Solutions                   |                              |

|-----------------------|-------------------------------------------|------------------------------|

| Looking for?          | to                                        | Microchip has the solution!  |

| Energy Savings        | Add Power Factor Correction               | PWM with 2 Time Bases        |

|                       | Incorporate Field-Oriented Control        | Free Software                |

| Noise Reduction       | Incorporate Sinusoidal Control            | Free Software                |

| Cost Reduction        | Remove Expensive Sensors                  | Free Software, 4 S&H ADC     |

|                       | Integrate PFC and Motor Controller        | PWM with 2 Time Bases        |

|                       | Integrate Controller on Motor             | 6x6 mm Small Packages        |

|                       | Easily Migrate to Other DSCs in Portfolio | <b>Optimized Feature Set</b> |

|                       | Remove Crystal                            | 1% Internal Oscillator       |

| Better Torque Control | Incorporate Field Oriented Control        | Free Software                |

|                       | Better Loop Response                      | Multiple S&H ADC             |

| Improved Reliability  | Migrate from Brushed to Brushless Motors  | Free Software                |

|                       | Noise Profile Diagnostics                 | DSP Resource On-chip         |

### Visit www.microchip.com/DSCMotor today

The Microchip name, logo and dsPIC are registered trademarks of Microchip Technology Incorporated in the USA and other countries. All other trademarks and registered trademarks are the property of their respective owners. © 2008 Microchip Technology Inc. All rights reserved. ME191Eng/03.08

# **Top Five Tips**

### Survival for Communications, Media and Entertainment Companies

### 01. What business am I actually in?

What exactly is my business offering? Who are my customers today and who will be my customers tomorrow? What do they want? Telcos need to understand that there is more to the next generation of networks than just technology rollout. Operators are starting to wake up to the fact that 'build it and they will come' is no longer true. Indeed, the ramifications run very deep within the company. As communications technologies begin to converge, companies are starting to compete with organisations that have previously been in complementary markets. This is leading to the question 'who am 1?' The confusion is both internal and external and needs to be answered, clearly defined and brand adjusted accordingly.

Sounds simple? Well, no. Some operators are lucky to have been seen more as a conglomerate offering a wide range of communications and have been accepted as such. Most operators aren't so lucky being seen as a media broadcaster or mobile operator leading a very expensive network that isn't being utilised properly.

Never think of a network as just technology rollout but understand that the whole company may need to be augmented behind it, fundamentally changing strategy.

### 02. Network sharing: Can it really deliver 40% savings on my network running costs?

Most of the business cases that we have seen for network sharing suggest that the long term benefits amount to around 25-35% of total network costs. Of course, the achievable savings depend very much on which elements of the network are shared.

What immediately springs out from these figures is the fact that the higher the share of new build in the overall costs, the greater the ultimate benefits. Intuitively this makes sense as it avoids all the messiness of consolidating legacy infrastructure, however it does raise an important point. The degree of alignment in the plans of the sharing operators for their network deployment will have a very significant impact on the ultimate benefits. Choosing your partner with care and forming the right 'pre-nuptial' agreement is vital to ultimate success. In reality however, few operators have the luxury of ignoring the legacy infrastructure so it is important to strike the right balance between the costs and complexity of consolidating legacy networks with the higher benefits of full sharing. Typically, we find that sharing around 2/3 of the infrastructure is about the best that can be sensibly achieved without agreeing a roaming arrangement, which is not possible everywhere.

### 03. How can I find a strategy for winning in wireless broadband?

With 3G networks lying largely empty, the industry is asking why 4G will be any different. The industry has learnt its lessons from 3G. It is making sure that the user experience, devices and services are going to be in alignment so that one does not fail the other.

But, there is one final elusive factor: demand. What is going to happen to drive demand for 4G? The answer is sitting in households all over the world, namely the digital native. These are the currently teenage generations who stack their communications using Facebook at the same time as watching TV and accessing YouTube. This is very different to the way anyone uses technology at the moment. When this generation enters the workplace and starts paying the bills then the demand for such user experience anywhere anytime will drive the demand for 4G. With this generation just around the corner, operators need to decide 4G strategy now. The clock is ticking.

### 04. Should I migrate my mobile customers from 2G to 3G and when?

Over the next five years, mobile operators face the challenge of increasing traffic demand while competitive pressure reduces voice revenues. For many, success will revolve around achieving cost efficiency while seeking new revenues from high speed data. Following a significant investment in 3G, operators are asking: "Is now the time to migrate customers to a network that can leverage more revenue while reducing OPEX?"

### 05. Do femtocells have a future?

The concept of the femtocell has caused excitement in the 3G infrastructure and operator world as well as with new players. From the concept perspective at least, it is quite revolutionary — equipment volumes of millions provided directly to consumers, short lifetime providing rolling market for manufacturers, connected to a backhaul funded by users, reduced customer churn beyond that provided by attractive handset bundles. It is ideally suited to solve 3G network problems of poor indoor coverage and capacity and to reduce network CAPEX and OPEX.

If it is to become a successful mass market product, a femtocell basestation must have a packed-up factory-gate cost of no more than £50 in volume production. Partitioning the design shows that this leaves only about £20 for the complex processing platform, compared with its macrocell counterpart that typically costs hundreds or thousands of pounds. The question is can a digital processing platform provide the processing needs for the femtocell product and meet this aggressive cost target?

This month's top tips were supplied by Chris Buist, Member of PA's Management Group at the PA Consulting Group. You can find out more by going on PA's website www.paconsulting.com/telecoms

If you want to send us your top tips on any engineering and design subject, please write to the Editor: svetlana.josifovska@stjohnpatrick.com

Selection of probes and accessories available

# See our new range of Oscilloscopes

### Features...

- USB 2.0/1.1 connectivity

- Dual Channel with External Trigger

- Up to 150 MHz Bandwidth

- Up to 200 MS/s Real-Time Sampling Rate

- Up to 20 GS/s Equivalent Sampling Rate

- Up to 1 MS Buffer per Channel

- Powered from USB

- Free Life-Time Software Updates

- 2 Year Warranty

Dataman Programmers Ltd. Station Road Maiden Newton, Dorset DT2 OAE UK Tel (01300) 320719 Fax (01300) 321012

### www.dataman.com

# AT THE HEART OF MODERN COMMUNICATIONS

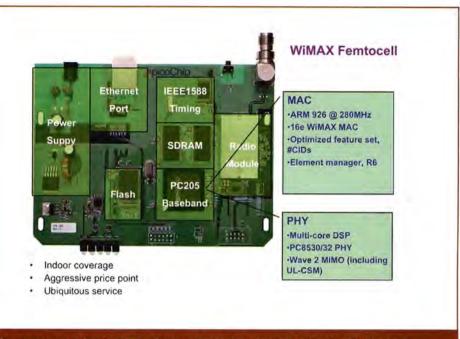

JUAN PABLO CONTI TALKS TO PICOCHIP, THE BATH-BASED SUPPLIER OF A DSP-TYPE OF ARCHITECTURE SUITABLE FOR DIFFERENT TYPES OF WIRELESS COMMUNICATIONS STANDARDS

Under the same style as Formula One broadcasts today include a variety of onboard video shots that show the action from the driver's point of view, come August 2008 TV audiences around the world will be able to enjoy a similar experience during the Beijing Olympics.

Of course, motor racing is not an Olympic sport, but sailing and rowing are. Boats competing in the coastal city of Qingdao and the Shunyi suburb of Beijing will be fitted with tiny cameras and transmitters that will be using a new form of mobile broadband wireless communications technology to relay the live images. Called McWiLL (Multi-carrier Wireless information Local Loop), the radio standard has been developed entirely in China by Xinwei Telecom Technology.

At the heart of each McWiLL base station, silicon developed by Bath, England-based DSP specialist picoChip will be taking care of the baseband processing functions.

Interestingly, it was supposed to be a DSP market leader that was going to be supplying this crucial part of the system. The original design stipulated the use of nine DSPs and two large FPGAs from that firm. However, when in November Xinwei revised the base station's technical specifications, it realised the eleven devices could actually be swapped by just two of picoChip's PC203 ICs, significantly lowering bill of materials and power consumption.

The story – which it must be said comes from picoChip – lends credit to two of the main marketing claims that are helping this fabless company make a name for itself in the semiconductor world: 1) that its massively multi-core chips are powerful enough to handle any wireless standard; and 2) that its package provides a more costeffective approach than conventional DSP alternatives.

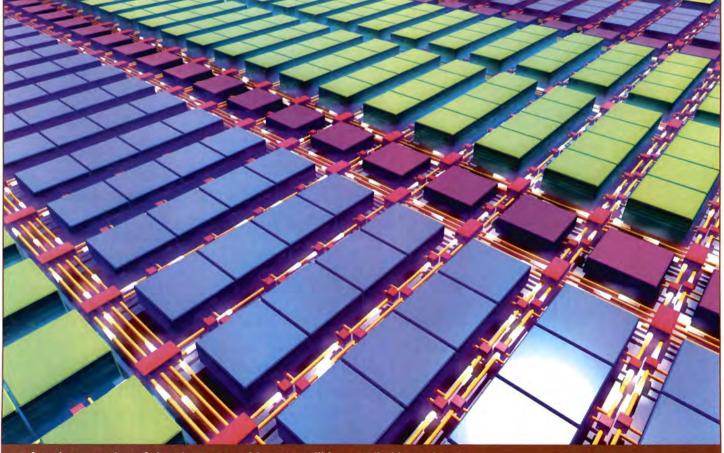

A fourth generation of the picoArray architecture will be unveiled later this year

### **COMPANY PROFILE**

### **Radio Focus**

The word 'package' is crucial here. The whole company has been built around a tightly knit integration of hard and soft offerings. On the hard side there's the picoArray architecture, an array of programmable elements optimised for highperformance signal processing. On the soft side there's a fairly complete development environment, specifically designed to help programme the family of picoArray-based ICs.

The development environment includes toolchains, libraries and software reference designs for some of the hottest wireless communication standards in town. WiMAX, WiBRO, HSDPA, HSUPA, WCDMA, TD-SCDMA, LTE... if it's radio-based, picoChip will tell you its architecture will tackle it.

In principle, there's nothing that would prevent a picoArray-based chip from addressing other types of DSP applications. However, the company is only interested in wireless, at least for the time being.

"The reason for the focus is purely commercial," says Rupert Baines, the firm's vice president of marketing. "When you're starting out you have to have a focus; you have to be able to focus on particular customers; you have to have application engineers with a deep understanding, because you're trying to break into a market and replace some incumbents, so you really got to focus all your intensity on one point to break through. Once you've got that breakthrough and you're established, you start having reference customers, your credibility builds up, money starts to flow and you can afford to broaden out, which is what we'll do over the next year or so."

Baines says the company has actually already got a few customers in other DSP areas, while he reveals ambitions to target, among others, the video and ultrasound markets in the near future.

There's another reason why picoChip is initially devoted to the wireless sector. Wireless is arguably the most dynamic of all electronic technologies. In some cases, standards change even faster than it takes to design, manufacture and distribute a communications product, based on their specifications. And that's where picoChip claims to have another strong advantage: the necessary flexibility to help OEMs and network operators keep up with constant modifications by deploying first and migrating later, purely by software.

Take WiMAX for example (a technology where, incidentally, picoChip's reference

Airspan is using picoChip silicon on its indoor and macro-cell WiMAX base stations

designs have come to be considered the industry standard). With WiMAX roll-outs now gathering pace all over the world, the technology is being improved all the time. The latest approved version (known as 'Wave 2') supports increased mobility and higher data rates using MIMO antenna configurations.

For the average WiMAX subscriber, each of these new technical additions is usually great news. They translate as faster Internet connections, using less wires and accessible from increasingly remote areas. For the average WiMAX equipment manufacturer, though, they mean rushing back to the drawing board to launch a new product family before your competitors do.

Last November, picoChip announced the first single-chip (PHY + MAC) WiMAX base station reference design to support Wave 2 and full IO-MIMO in both downlink and uplink channels. Crucially, it will offer OEMs currently using Wave 1 designs, such as Airspan or Fujitsu, a seamless software upgrade to the new version.

"There are more WiMAX base stations using us [picoChip's products] than using any other single architecture, but without us WiMAX would still be happening," Baines acknowledges. "Some people's base stations would cost a bit more money; some would be a bit less flexible. One probable difference would be that there'd be less competition. Because what we do is we enable Tier-2 [companies] and people with interesting ideas but not huge development teams to use us to get into the market. We reduce the barriers to entry."

### **COMPANY PROFILE**

But it's not just Tier-2 firms that are turning to picoChip's WiMAX expertise. Intel (apart from being one of the firm's key investors together with Pond Venture Partners, Atlas Venture, Highland Capital Partners, Scottish Equity Partners, Rothschild, AT&T and Samsung) is also a picoChip customer. This may sound somewhat confusing given Intel's much-publicised own WiMAX ambitions.

"Intel has got a lot of different WiMAX programmes," Baines clarifies. "Their own product development is focused on chips that go into PCs. But they do also make other products. One of them is a standalone card – effectively a base station card – and they use us for that."

### The Femtocells are Coming

Together with WiMAX, the other wireless sector where picoChip is heavily involved in is cellular communications. In particular, the company is seen as one of the driving forces behind what many believe is the next big thing in the mobile phone industry: femtocells.

The femtocell concept is quite simple. As operators migrate an increasing proportion of their customer base from 2G to 3G, the inherently higher frequencies at which 3G networks operate make indoor coverage even patchier than it already is with 2G. This is problematic for various reasons:

Airspan is using picoChip silicon on its indoor and macro-cell WiMAX base stations

The company's femtocell architecture can be applied to both cellular and WiMAX air interfaces

### "THE INHERENTLY HIGHER FREQUENCIES AT WHICH 3G NETWORKS OPERATE MAKE INDOOR COVERAGE EVEN PATCHIER THAN IT ALREADY IS WITH 2G"

subscribers use their mobiles mostly when they are indoors; operators are banking on an increasing use of data services on their 3G networks; and competition from voiceover-WiFi providers is intensifying.

Femtocells – which were first demoed by picoChip at the 3GSM 2005 event – not only address these challenges, but they also throw in a few collateral benefits. Essentially a miniature, indoor 3G base-station the size of a paperback book that plugs into the subscriber's broadband line, a typical picoChip femtocell device will support up to four users.

As soon as one of them enters the home, the femtocell will automatically take over from the macrocell network. Users are then guaranteed a wireless data link of up to 7Mbit/s using an HSDPA-enabled laptop or phone.

The novel network architecture opens up a much more efficient way of managing traffic for the operators. Additionally, it helps them offload their two most expensive items in terms of operating expenses: base station backhaul and electricity, both of them now paid by the subscriber. This puts operators in an ideal position to aggressively package and price femtocell-based voice and data services.

"The interesting thing is that this is a market being driven by the operators," says picoChip's Baines. "It's very much people like Vodafone and Telefónica [in Europe], Sprint [US] or SoftBank [Japan] who are pushing it and making it happen, far more than being a technology pushed by suppliers. This is simply because it solves a very big problem for the operators. As soon as they realise this is something that works they're very keen to get it in their networks."

ABI Research is predicting some 70 million femtocells will be installed worldwide by 2012, with 150 million people using them. Considering the direct and indirect financial benefits they will bring, operators will most likely subsidise the roughly €120 cost of each box.

So when can we expect to see femtocells being deployed on a noticeable scale? Baines points out they're already commercially

### **COMPANY PROFILE**

available in some places. Sprint, for example, has been marketing them in a few of its domestic markets since the second half of 2007. "But it will really be during 2008 that operators will be making their first deployments," he predicts.

He should know. His company's silicon and software are already being integrated into the designs of some of the early OEMs that have started to address the femtocell market, such as ipAccess (which supplies Thomson), Ubiquisys (supplies NEC and Motorola) and Axiom.

#### The Road Ahead

Ever since it launched the picoArray architecture at the end of 2002, the Bath firm has introduced a new generation of semiconductors approximately every two years, with the second generation launched at the end of 2004 and the third, and so far last, one making its debut in 2006. "Does that mean we're going to be seeing a fourth generation launched at some point in 2008?" I ask. "Yes," Baines replies, and after a short pause he laughs at the forced shortness of his answer.

"And what kind of performance can we expect from it?" I try again. "I'll tell you when we announce it," the predicted

#### response.

But you can certainly expect a jump in processing power, reduced power consumption and more flexibility. With giants TI and Freescale both showing increasing interest in the multi-core DSP space picoChip still dominates, the company can't really afford to rest on its laurels.

"Hmm... yes," Baines replies when I ask him whether that's the main threat picoChip currently faces. "I mean, we compete with some very well-established, very strong players, and we've got to stay ahead of them. Texas Instruments, Freescale, Xilinx are all very good companies with some very smart people. So we have to keep pushing and keep fighting to stay ahead.

"I think we've set a very aggressive pace, addressing a lot of different markets and it's challenging to keep up with that. We're working on many different things, so [what we need] is just the keeping going and not screwing up, in a sense."

They're not the only ones who'll be needing that. The sailing and rowing Olympians in Beijing will also try to "keep going and not screwing up" later this year. While the rest of us will be following their actions attentively, almost as if we were inside their boats with them too.

The small fabless semiconductor maker from Bath has developed one of the world's most powerful DSPs

### picoChip in brief

Founded: September 2000 by Peter Claydon and Douglas Pulley Headquarters: Bath, England CEO: Guillaume d'Eyssautier Employees: 130 Annual sales: Undisclosed Net income: Undisclosed Capital investment funding: \$71.5m (four rounds)

### Time to quit smoking...

Smoke and poisononus fumes often pose a far greater threat to life and property than a fire itself.

Our LSHF cables are LSHF throughout, insulation and sheath, and do not emit toxic gases in the event of fire.

### Low Smoke Halogen Free Cabling

Call our sales team for your free copy of our LSHF buyers guide

- Tel: 01727 840 841

- www.fscables.com

- sales@fscables.com

### EuP DIRECTIVE

Gary Nevison is chairman of the AFDEC RoHS team, and Customer Support Manager, Legislation and Environmental Affairs at Premier Farnell. As such he is our industry expert who will try and answer any questions that you might have relating to the issues of RoHS, WEEE and REACH. Your questions will be published together with Gary's answers in the following issues of Electronics World.

# ECO-DESIGN OF ENERGY USING PRODUCTS

he Eco-design of Energy using Products (EuP) Directive will require manufacturers to carefully consider environmental aspects when designing and developing new products. Currently studies are underway to define what measures are required, but the European Commission (EC) has yet to make any firm decisions on the new legislation that will impose eco-design criteria.

Typical examples of products that could be affected include: any mains powered product that has a standby mode – e.g. printers, scanners, etc; any mains powered product that does not have an off-switch that disconnects the mains power; lighting equipment – office, domestic and street (ballasts, bulbs, etc); electric motors rated between 1 and 150kW; some external power supplies and battery chargers; air compressors and vacuum cleaners among others.

The directive mainly affects equipment designers. The EC will impose measures that will place requirements on products that will necessitate on-going improvements in their eco-design. The requirements for each product type will be different, however, some general guidance on eco-friendly new product design is known.

Products with a standby mode are likely to be specified a maximum power consumption level in this mode. Standby mode is typically used where equipment needs to be reactivated remotely (by infra-red for example), or is required to carry out a continuous function such as displaying a clock.

The maximum power consumption in standby mode depends on the equipment's function. The figure being proposed for products that use standby as a re-activation function only, for example televisions, microwave ovens and computer monitors, is 1 watt. It is planned that this figure will be reduced to 0.5 watts after a time. Equipment to which the directive applies will need to be designed to ensure that these values are not exceeded. This requirement has farreaching implications as every function within a product's circuitry will need to be reviewed in order to determine how the overall standby power consumption can be reduced.

Many products cannot be completely shut down as the off switch disconnects the input power supply from other parts of the equipment but does not disconnect the power supply from the mains. Termed 'off-mode', the EC is proposing to restrict power consumption of equipment in this state to initially 1 watt and then two years later, to 0.5 watts.

The overall power consumption of many products will be controlled either by imposing restrictions with specific consumption limit values or by having to display an energy rating label that is clearly visible to consumers/users.

Energy ratings are already used on light bulbs, washing machines and refrigerators and have proved a great success in making consumers carefully consider energy consumption when they purchase new products. Most products currently on the market achieve the top rating as a result of improvements already made by manufacturers. This fact is not very useful to consumers and it does not give an incentive to reduce power consumption still further. Therefore, one proposal is to change the criteria used for these ratings so that the power consumption of top rated products is lower than is currently used and so that only the very best products can achieve the top rating. This will give an incentive to manufacturers to make further improvements to their products.

For example, it is proposed that new energy ratings will be developed for fluorescent lamps that will identify the best performing products; currently nearly all have the top 'A' rating. Another proposal is to regulate the energy efficiency of power supplies and battery chargers with obligatory specified minimum efficiency values. This will directly affect power supply design and push forward technical advances in the power electronics sector.

So-called 'active power management' is also being proposed by the EC. This would require equipment to switch itself into standby mode if it is not used for a given period of time. A variety of products are unnecessarily left permanently switched on; good examples are computers, printers and lighting. In some products, switching to standby is impractical but huge power savings can be made by switching off individual functions that are not in use.

Clearly specified and labelled expected life and other similar information may be required for certain new products. This is being proposed for items such as lamps to encourage designers to make their designs last as long as possible and in so doing have a reduced impact on the environment

Eco-design of EuPs could restrict the use of hazardous materials, for example a recently completed study into office lighting recommended reducing the maximum mercury content of fluorescent lamps below that currently permitted in the RoHS Directive.

Recently, the EC has announced the next batch of product categories for review over the next three years. As we move forward, new EuP implementing measures will target energy consumption but could also affect many other aspects of equipment design. This will make it advisable for designers to carefully consider how their new product developments perform in terms of minimising power consumption, making recycling easier plus reliability and life expectancy.

Please email your questions to: svetlana.josifovska@stjohnpatrick.com marking them as RoHS or WEEE.

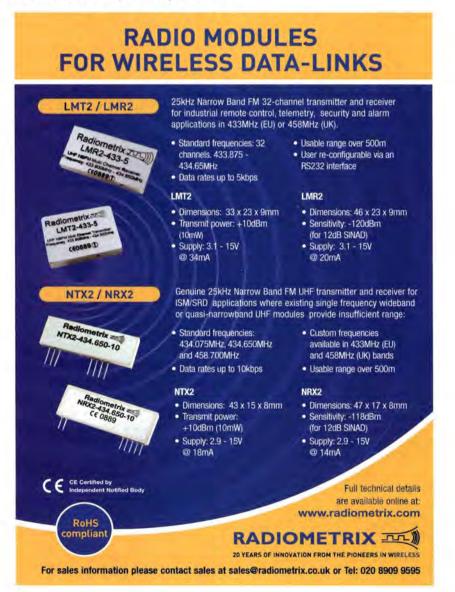

### Column THE TROUBLE WITH RF...

### SEEING THROUGH THE WIRELESS TRENDS

nyone currently working in the low power radio industry cannot be unaware of the arrival on the scene of a new species of "network protocol" radio modules. The most familiar and widely publicised of these are probably the Zigbee devices. Originating with a specification released in 2004 (derived from work begun as early as 1998) by the Zigbee Alliance, a consortium of over a hundred companies

THERE IS AN OLD SAYING THAT GOES: "AN ENGINEER CAN DO FOR A PENNY WHAT ANYONE CAN DO FOR A POUND". IT'S STILL TRUE TODAY.

of different sizes including some major silicon vendors, these radios have been intensively marketed as, apparently, a universal wireless solution.

There are a range of vaguely similar imitators (such as Z-wave, Wibree, Insteon and PWN to name only a few), some of which are completely novel while others borrow 802.15.4 radio hardware to run different application firmware stacks. (Strictly speaking, the name "Zigbee" refers to an application and network layer specification, which in turn calls for IEEE 802.15.4 compliant radio hardware. Some applications actually use this type of radio hardware without the full software stack, as simple, conventional short range links.)

With the availability of improved, cheaper RF transceiver devices and increasing levels of advertising, many users are coming to consider such 'famous name' network specification modules as the only solutions for all and any short range wireless functions, and the suppliers of them do nothing to contradict this opinion.

There are many buzzwords abound, including "wireless sensor networks" and "wireless personal area network" devices that are on offer. But what do they actually do, in comparison to a 'traditional' radio system?

The simplest case radio link is a "point to point" application. A device either sends commands to a distant unit (imagine a light switch controlling a light), receives data from it (remote reading of, say, a tide-gauge), or both.

When one 'base unit' communicates with multiple 'out-stations' (consider the monitoring and control of pumps and valves in a water purifying plant) then the radio system has a "star" configuration. Communication can be initiated strictly by the base unit only ('polled' networks) or out-stations can initiate transmissions (either randomly, with retries and possibly 'listen before send' to deal with collisions in 'low duty cycle' systems, or in specifically allocated time slots for 'beacon synchronised' networks).

Star networks (or "point to multi-point" systems) are probably the most common form of low power radio implementations. These are simple to implement and easy to understand techniques. They are typical of customer designed, proprietary ISM band solutions used for many decades. While they hardly fall into the category of wireless networks, they do provide more than adequate facilities for a very large number of applications.

All the above architectures are, however, limited by the range of the basic wireless link: they communicate over only one radio 'hop'. Where the 'master' base

by Myk Dormer

unit communicates with one or more distant subordinate bases or 'repeaters', which in turn each communicate with their local group of out-stations, then a "tree" architecture has been formed and we can see the system complexity is significantly increasing.

The simplest version of this network would be a base sending to a repeater, which in turn sends to an out-station. In this case the communication link is over two radio link hops, increasing range, or allowing the placement of the repeater to cover an awkward area where a direct path from the base unit is blocked by terrain.

Even this simple tree network requires extra information to be added to the data burst (so as to prevent multiple responses where the base is in range of both the repeater and the out-station), while particular care is needed in handling 'acknowledge' protocols across the multiple hops. As multiple repeaters and multiple out-stations are added, the complications multiply also and the network protocol must be made more sophisticated.

Methods must be included to prevent 'rings' of repeaters forming (that will pass a single message around for ever), while

### THE TROUBLE WITH RF... Column

traffic synchronisation is needed to stop the collision when two repeaters receive and re-send a burst from the same outstation. Unique 'message identifiers' must be added to the packets and a 'retransmission history' included.

These problems are well understood, as they occur in existing 'packet radio' nets (and in the traffic handling methods used on the internet) but they cannot avoid adding some overhead to the system. Either complex auto-configuring methods are needed (incurring time delays and eating up processing power and bandwidth), or the network must be manually set up, possibly resulting in an inflexible structure, as well as adding to the user's workload.

The final level of complexity is reached in the "mesh" network. In this case the rigidly-defined repeater to out station hierarchy of the tree structure is dispensed with and all out-stations (or "nodes") can communicate with all the other nodes in range. This eliminates the inherent 'brittleness' of a tree network (in that the loss of a single repeater can isolate a whole 'branch' of out-stations) as theoretically, in an ideal ('fully connected') mesh network, there will be multiple communication paths for each hop, so local interference or the loss of a given node ought not disable the network.

Some mesh systems retain a 'master' unit that co-ordinates the network operation and set-up, while other systems go even further and implement the same communication functions in every node (these are referred to as 'peer to peer' networks.)

Simplification can be had by using a mixed approach, with some nodes capable of 'full' communication, while others can receive or originate a data packet, but are incapable of relaying traffic from other nodes. (This is the system adopted by Zigbee, with a base unit 'co-ordinator', communicating to full function 'routers' and reduced function, lower power 'end devices'.)

All sounds pretty impressive, doesn't it, but it comes at a cost and that is in complexity. A lot of data traffic, much of it redundant, is passed by the nodes (increasing power and overall bandwidth usage), while the amount of processing required to set up and to operate the network is daunting (a simple, reliable point-to-point link can require only a few hundred bytes of code, on a very low end processor. Full Zigbee stack implementations are quoted as requiring between 30 and 100kbytes of code).

Some applications really do need the facilities that a mesh network offers and assuredly some of those will fall into the area of low power radio. But there are a lot of tasks where only a few bytes worth

of information are required to be sent over not-inconsiderable distances, under very tight available power constraints.

These are places where simplicity still wins over complexity and where a little effort taken to implement a good analogue radio link is worth any amount of high level coding.

There is an old saying that goes: "An engineer can do for a penny what anyone can do for a pound". It's still true today.

Myk Dormer is Senior RF Design Engineer at Radiometrix Ltd www.radiometrix.com

### 2008: THE YEAR OF POLYMER ELECTRONICS?

### **DR ALEC READER,** DEVELOPMENT DIRECTOR AT INNOS, SAYS THAT THIS YEAR BEGINS THE UPWARD CURVE FOR POLYMER ELECTRONICS; BUT, ARE YOU READY FOR IT?

he physical limitations of silicon have long been a concern for innovators creating groundbreaking intellectual property (IP) for the next generation of electronic devices. Many innovators and early adopters that I speak to have predicted that 2008 will be the year that organic (or polymer) electronics really take off due to their benefits in a number of applications over silicon, but it is crucial that the industry prepares right now.

Advances in organic electronics (based upon semiconducting polymers) have already seen several firms secure pilot line production contracts in 2007, to produce the first devices for eventual sale to market. Polymer electronics' inherent low production cost, portability, aesthetics and, ultimately, the capacity for formable logic and storage circuits whilst staying robust, ensure cheaper devices with a wide range of applications, particularly in the lucrative mobile device market.

In fact, it is the sheer 'flexibility' of polymer electronics that can and will change the market. Semiconducting polymers lend themselves to the fabrication of flexible displays, a market predicted by the electronics industry analysis firm EMSNow, to reach a value of \$60m by 2013. Meanwhile, rollable display technology uses many of the same components and characteristics of flexible displays but requires a far greater degree of curvature and resilience than is typically required by a flexible display.

The development of prototype rollable displays designed specifically for use in mobile devices (e.g. telephones) has given way to the signing of commercial deals to produce the first range of product applications in the race to the retailer's shelves. These rollable displays – some able to challenge the circumference of a pencil when completely rolled – have enabled the future production of integrated screens for mobile devices that are physically much larger than the device itself.

Displays of this nature require an appropriate front plane and back plane in order to gain this high flexibility. Developments by innovators so far have been heavily dominated by non-emissive technology, where light is reflected or absorbed as opposed to emitted, with the prime incentive being its low energy consumption. Consumers of mobile devices increasingly expect maximum functionality and longer battery life; non-emissive screens combat this by using low current to generate and, therefore, extend the time before the need to charge the battery.

For example, one of the key front plane technologies is electrophoresis, which allows the separation of black and white particles within individual pixel cells in a display according to their size and charge, using an electric field (specific arrangements of pixel cells will give way to full colour displays). Coupling this with a mature technology such as organic TFT (thin film transistor) for the flexible backplane could see it become one of the most effective methods of creating a rollable display.

There is, of course, huge potential for the growth of emissive front plane technology such as OLED in the future, which unlike nonemissive requires no backlight to view in low light conditions, by using light emitting photons. Typically though, this technology is far more suited to devices or consumer products using a mains power source, such as a television, as it is relatively power-hungry. It is not particularly suitable for mobile devices when compared with non-emissive displays, as the lifetime of some materials and batteries may not sustain intensive everyday use.

The outlook for polymer electronics is indeed an exciting one; Columbia News Service has predicted that the market as a whole will reach \$12.5bn in 2012, to double by 2025 according to IDTechEx.

Year 2008 may very well be the one that the technology starts seeing substantial revenues; however, I strongly believe that innovators need to start to exploit applications as soon as possible to ensure their position as a forerunner in the race to market.

Rollable display technology uses many of the same components and characteristics of flexible displays but requires a far greater degree of curvature and resilience BY MATTHEW HAUSE, PRINCIPAL CONSULTANT, ARTISAN SOFTWARE TOOLS SHOWS HOW OMG SYSML ARTIFACTS CAN BE USED ON MISSION-CRITICAL APPLICATIONS TO SPECIFY THE REQUIREMENTS FOR SOLUTION SPACES SUCH AS SOFTWARE AND HARDWARE TO PROVIDE TRACEABILITY AND HANDOVER

# DESIGNING MISSION-CRITICAL SYSTEMS USING OMG SYSML

ack in September 2007, the Object Management Group (OMG) announced that OMG SysML v1.0 had been issued as an Available Specification.

The OMG SysML specification was developed in response to the joint Request for Proposal issued by the OMG and INCOSE (the International Council on Systems Engineering) for a customised version of UML 2 designed to address the specific needs of system engineers. Its customisation for systems engineering supports the modelling of a broad range of systems which may include hardware, software, data, personnel, procedures and facilities.

In developing OMG SysML, the goal was to provide a "standard modelling language for systems engineering to analyse, specify, design and verify complex systems, intended to enhance systems quality, improve the ability to exchange systems engineering information amongst tools and help bridge the semantic gap between systems, software and other engineering disciplines".

Mission-critical applications, in particular, need to take a holistic approach to development. Using Artisan Studio's comprehensive OMG SysML Profile, which makes use of its powerful domain-specific profiling capability, this article shows how OMG SysML artifacts can be used on mission critical applications to specify the requirements for solution spaces such as software and hardware to provide traceability and handover.

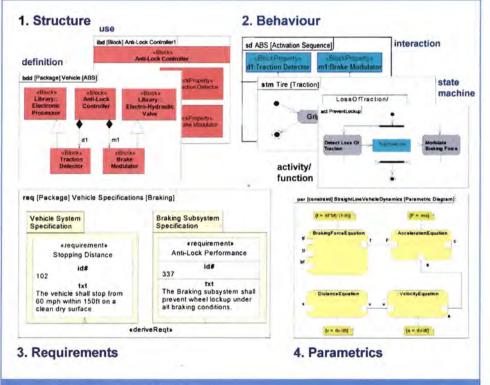

Figure 1: The four pillars of OMG SysML

#### **OMG SysML Structure**

OMG SysML includes diagrams that can be used to specify system requirements, behaviour, structure and parametric relationships. These are known as the four pillars of OMG SysML. An example of these different diagrams for an automotive ABS system is shown in

### Figure 1.

The system structure is represented by

block definition diagrams and internal block diagrams. A block definition diagram describes the system hierarchy and system/component classifications. The internal block diagram describes the internal structure of a system in terms of its parts, ports and connectors. The package diagram is used to organise the model.

The behaviour diagrams include the use case diagram, activity diagram, sequence

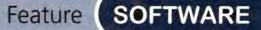

### Figure 2: Requirements diagram

### Figure 3: Block definition diagram

diagram and state machine diagram. A usecase diagram provides a high-level description of the system functionality. The activity diagram represents the flow of data and control between activities. A sequence diagram represents the interaction between collaborating parts of a system. The state machine diagram describes the state transitions and actions that a system or its parts performs in response to events.

The requirement diagram captures requirements hierarchies and the derivation,

satisfaction, verification and refinement relationships. The parametric diagram represents constraints on system parameter values such as performance, reliability and mass properties to support engineering analysis.

Figure 1 makes use of cross-cutting constructs. These apply to both structure and behaviour. Cross-cutting constructs support concerns that cut across the different views and may be addressed by all or disparate parts of the model. These constructs take the form of allocations, requirements and parametrics.

#### Requirements in OMG SysML

Requirements traceability is an essential part of mission critical applications. For DO-178B, for example, traceability must be provided between system requirements and high-level software requirements, high and low level requirements, low-level requirements and tests, tests and code for structural coverage, and from top down and bottom up.

The requirement diagram is used to integrate the system models with text-based requirements that are typically captured in requirements management tools, to facilitate the required traceability.

The UML containment relationship is used to decompose a requirement into its constituent requirements. The «deriveReqt» and «satisfy» dependencies describe the derivation of requirements from other requirements and the satisfaction of requirements by design, respectively. The «verify» dependency shows the link from a test case to the requirement or requirements it verifies.

In addition, the UML «refine» dependency is used to indicate that an OMG SysML model element is a refinement of a textual requirement, and «a copy» relationship is used to show reuse of a requirement within a different requirement hierarchy.

The «rationale» concept can be used to annotate any model element to identify supporting rationale including analysis and trade studies for a derived requirement, a design or some other decision. **Figure 2** shows the requirements flow down for an INU/GPS component.

More specialised requirement types can be designated using specialisation of the «requirement» stereotype. Each requirement has a unique identifier shown next to the id# tag and the text of the requirement is shown in the compartment labeled "txt" in the lower part of the class box.

The format shown is only one of a number of possibilities and ergonomic profiling can be used to modify the display format to correspond to the needs of the audience. Artisan Studio 6.2 has been used in these examples but the exact capabilities for this type of feature will depend on the actual tool being used. Additionally, requirements and their relationships can be shown on other diagrams.

Tools that provide the functionality to import, export, and synchronise requirements

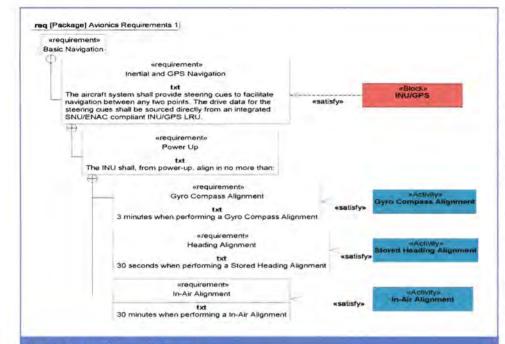

### SOFTWARE Feature

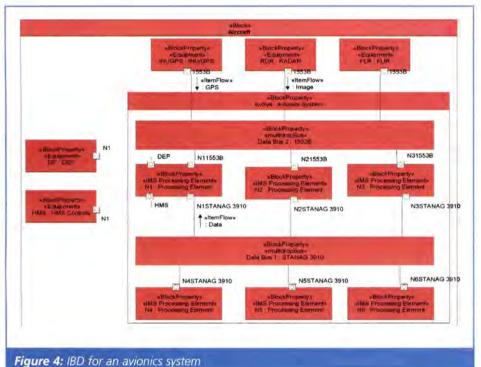

### rigure 4. Ibb for all aviolitics system

and their relationships between the OMG SysML model and an external requirements management tool will allow developers to perform requirements traceability in the tool while taking advantage of the features provided by specialist requirements management tools. Traceability reports can normally be generated directly from the integrated model in a format compatible with DO-178B.

#### Structure

A clear description of the system and its environment is essential for mission-critical applications. OMG SysML provides block diagrams to support this. The OMG SysML «block» is a general purpose hierarchical structuring mechanism that abstracts away much of the software-specific detail implicit in UML structured classes.

Blocks can represent any level of the system hierarchy including the top-level system, a subsystem, or logical or physical component of a system or environment. An OMG SysML block describes a system as a collection of parts and connections between them that enable communication and other forms of interaction. Ports provide access to the internal structure of a block for use when the object is used within the context of a larger structure. OMG SysML provides standard ports which support client-server communication (e.g. required and provided interfaces) and FlowPorts that define flows in or out of a block.

\* Structured diagram types: Two diagrams are used to describe block relationships. The Block Definition Diagram (BDD), similar to a traditional class diagram, is used to describe relationships that exist between blocks. The Internal Block Diagram (IBD) is used to describe block internals.

An example of a block definition diagram is shown in **Figure 3**. The example of an avionics system is represented as a block composed of other blocks, including several processing elements, 24V power and two buses. The role names on the association ends correspond to the parts on the IBD.

The internal structure of an avionics system is shown in **Figure 4**. Each of the components has a number of flow ports that describe what can flow in and out. These are then connected to other compatible ports to enable the required flows in this context. The arrows on the connectors represent item flows that correspond to physical or logical items that actually flow through the system and whose properties can be constrained in parametric models.

\* Allocations: The OMG SysML allocation relationship is used to allocate one model element to another. Allocation is the term used by systems engineers to denote the

organised cross-association (mapping) of elements within the various structures or hierarchies of a user model.

Often this is the allocation of function to form, such as the deployment of software on a hardware platform, or a use case to an organisation or system entity or a logical to a physical entity.

Allocations can be used early in the design as a precursor to more detailed rigorous specifications and implementations. The allocation relationship can provide an effective means for navigating the model by establishing cross relationships and ensuring the various parts of the model are properly integrated. The integration of the software and hardware models means that SIL levels for the various parts can be assigned and verified to ensure a consistent implementation. Hardware/software interfaces can also be verified, as well as architectural constraints, thus ensuring traceability and change analysis.

Additionally, studies are being done to determine if Goal Structuring Notation (GSN) can be integrated into a model in a similar way as requirements described above. GSN provides a graphical means of expressing a safety case. Creating links from the model elements to the GSN safety case elements provides direct traceability and the possibility of modular safety cases, using OMG SysML packages. This creates savings in the time required to build the safety case, and therefore money.

#### **Robust Language for Modelling**

The extensions made to UML 2 in the OMG SysML Profile provides systems engineers with a robust language for modelling systems that include models of requirements, behaviour, structure and parametrics.

At the same time, the profile's extensive reuse of UML facilitates a much smoother flow down from systems engineering to software engineering than otherwise possible.

### **References:**

A variety of technical papers and a summary of OMG SysML are available from http://www.artisansw.com. Further, specific information on the OMG SysML v1.0 specification available at http://www.omgsysml.org/.

# MODEL-BASED DESIGN FOR MECHATRONIC SYSTEMS

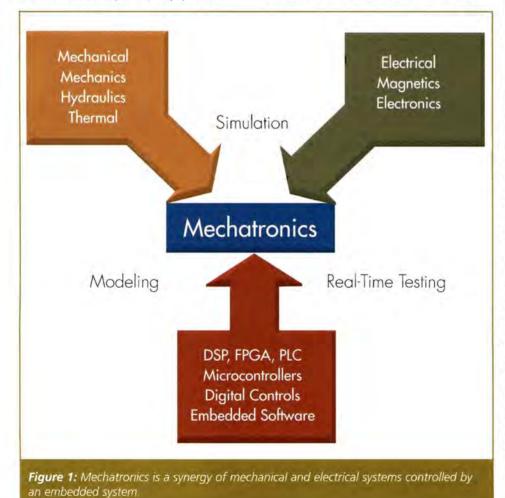

ost engineers are surprised to learn that the term mechatronics is nearly 40 years old. It was first used in1969 by Tetsuro Mori, an engineer at the Yaskawa Company, to describe a system composed of mechanical and electrical elements that is controlled by an embedded system (**Figure 1**).

In today's world it is rare to find electromechanical devices without some kind of embedded system. The intelligence from an embedded system delivers enhanced performance, reduced energy consumption, better reliability and safer operation, which are key differentiators and value drivers for a piece of equipment. The benefits of an embedded system come at a price. As mechatronic systems take advantage of more powerful microprocessors, which provide the intelligence for embedded systems, the interaction between hardware and software becomes more complex. Managing this complexity can prove challenging to hardware and software engineering teams, who state requirements, describe problems and test and implement solutions in different ways.

In addition, engineers must design closed-loop control strategies to compensate for electromechanical interactions and external disturbances, as

TONY LENNON, INDUSTRY MARKETING MANAGER AT THE MATHWORKS EXPLAINS THE BENEFITS AND WHY MODEL-BASED DESIGN IS THE TOOL OF CHOICE FOR SYSTEM-LEVEL DESIGN OF MECHATRONIC SYSTEMS

well as incorporate open-loop supervisory control for operational requirements, such as start-up and shutdown, personnel and equipment safety, and fault detection and remediation.

In most traditional design approaches, engineers test software on hardware prototypes, addressing software validation very late in the development process. Errors found in hardware or software at this stage create costly delays and may be time consuming to trace back to their root cause. Errors related to incomplete, incorrect, or conflicting requirements may even necessitate a fundamental redesign.

### Improved Development Using Model-Based Design

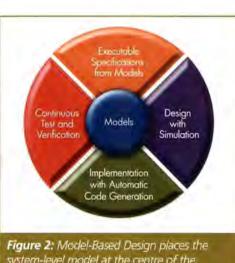

Model-Based Design (**Figure 2**) simplifies the development of mechatronic systems by providing a common environment for design and communication across different engineering disciplines. Model-Based Design extends the computer-aided engineering (CAE) world with an additional perspective on system-level design.

Just as computer-aided design (CAD) provides a geometric or static description of

system-level model at the centre of the development process for mechatronic systems

equipment, Model-Based Design incorporates the dynamics and performance requirements needed to properly describe the system. Because this approach is software driven, engineers can fluidly investigate competing designs and explore new concepts without the overhead of extensive hardware investment.

Engineers can continuously test the design as it evolves, checking it against requirements and finding mistakes earlier in the development process when they are easier and less costly to correct. In addition, Model-Based Design automates code generation for the embedded system by eliminating the need to hand code the open and closed-loop control algorithms.

Model-Based Design uses a system-level model that defines an executable specification by uniquely describing the natural and controlled behaviour of the equipment in a mathematical form. Engineers can execute the model by simulating the actual dynamics and performance of the system. The model specifies an unambiguous mathematical definition of the expected performance of the mechatronic system. As an executable specification, the system-level model provides a clear advantage over written documents, which, because they are subject to interpretation, can lead to requirements that are missing, redundant, or in conflict with other requirements.

Written requirements will always exist, but engineers can link their electronic formats to the system-level model and help establish compliance to standards such as ISO 9001 or IEC 61508. Tracing requirements from the written specifications to the system-level model clarifies how the engineer interpreted the requirement. Electronic links between requirements and the model let engineers connect test criteria to test cases used throughout the development process.

Feature

### Developing the System-Level Model

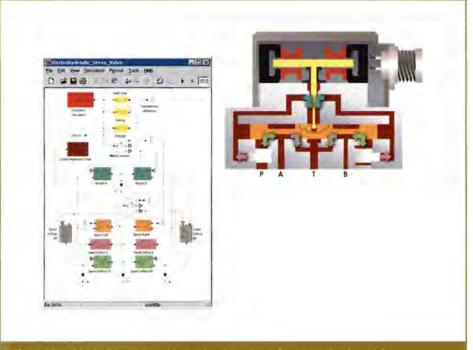

A block diagram is a natural approach for expressing a system-level model (**Figure 3**). The model has inputs - signals provided by external agencies, and outputs - measures of what the system is actually doing. The inputs and outputs represent real values, such as voltage, temperature and pH.

Inside the model, the blocks represent mathematical operations between the input and output signals of the model. Some blocks, called the plant or process, represent the natural behaviour of the mechatronic system. For example, the model may contain a block representing a motor. The mathematical model of the motor may be fairly simple, just taking a voltage input and converting it to an output torque.

The motor model complexity can increase by adding more inputs to the model, such as noise in the voltage, or by adding more parameters, such as temperature and magnetic saturation affects. A single block or a group of blocks, filtering and processing signals based on output errors or events occurring in the model, can represent the compensation or control in the system.

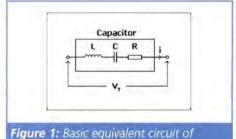

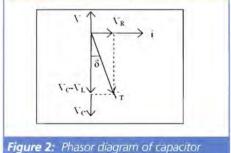

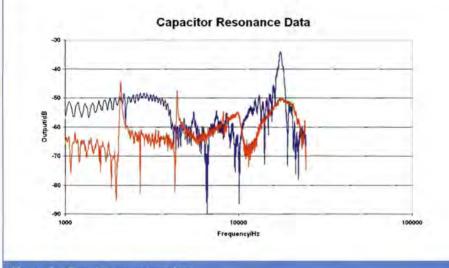

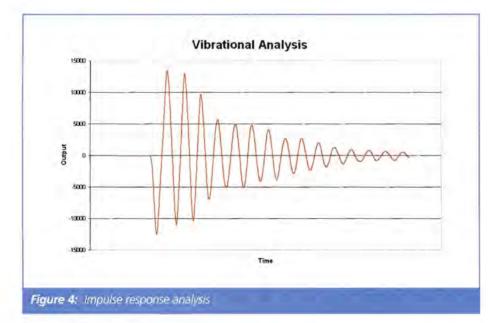

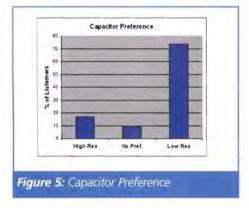

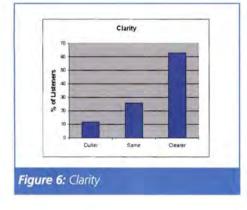

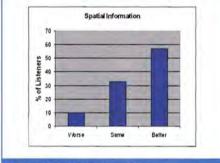

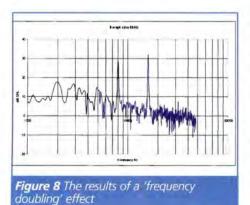

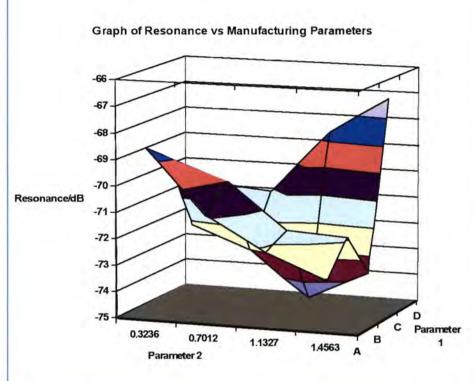

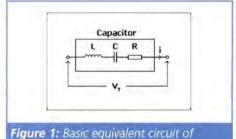

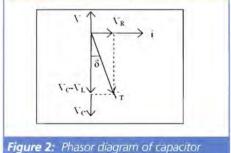

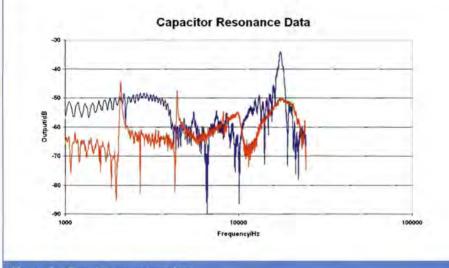

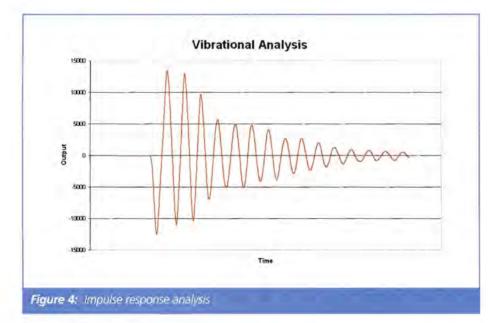

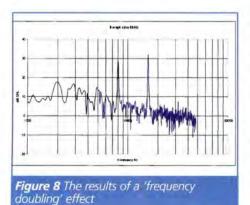

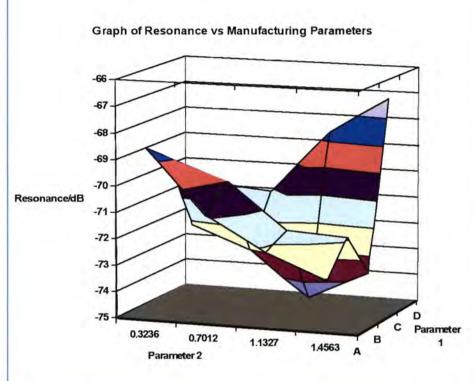

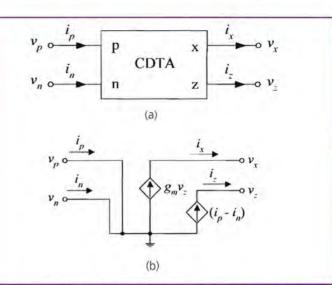

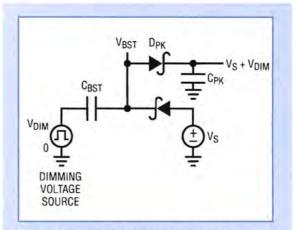

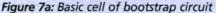

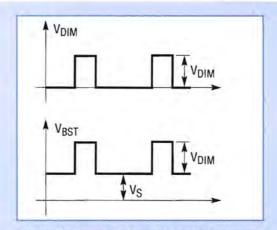

The basis of a system-level model is a lumped parameter mathematical model that describes the physics of the system. Ordinary differential equations (ODEs) and differential algebraic equations (DAEs) express the input-to-output relationship of the mechatronic systems.